筑永EDA通用全流程解决方案

Scalable Physical CAD for FPGA & ASIC

墨林(Marine)综合器

高性能的EDA前端综合工具,专为FPGA和ASIC设计而生,致力于提供行业领先的综合解决方案。其强大的功能和卓越的性能能够显著提升设计效率,加速产品上市时间。

FPGA&ASIC EDA前端综合

- 支持标准:全面支持行业最新标准IEEE-1800 2017 SystemVerilog,包括多库和XMR综合支持。

- 多样性网表:支持将Verilog设计展开至Gate-Level和Lut-Level Verilog格式网表,分别满足ASIC和FPGA用户需求。

- DW库支持:支持等效的DesignWare综合仿真库,加速产品上市时间,降低开发成本,提高设计可靠性。

- 多线程技术:采用跨模块多线程综合技术,在8线程下实现4倍速度提升。

- 增量编译:引入增量编译技术,综合性能平均提升高达20倍。

- 优化解决方案:提供针对时序性能及面积/成本优化需求的领先解决方案。

- Tcl脚本支持:支持Tcl脚本编写,实现自动化综合,提高设计效率和一致性。

- 自动优化:自动执行前端Memory综合和优化、Datapath综合和优化,并提供可选的FPGA Technology Mapping功能。

- 状态机优化:通过FSM Compiler和FSM Explorer,实现RTL中有限状态机的自动提取和优化。

- 代码检查:提供准确、完备的Verilog和SystemVerilog源代码语法和语义检查功能,确保设计的正确性和稳定性。

- 名称保留:提供可选的RTL名称保留功能,确保优化过程中保持设计意图和结构。

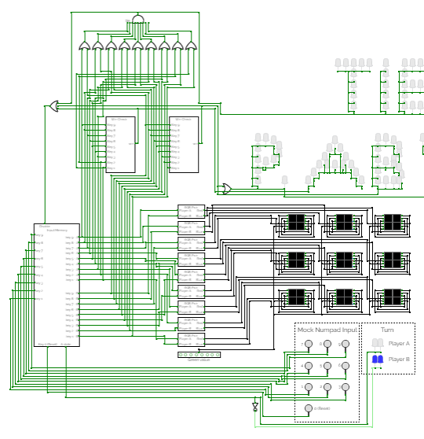

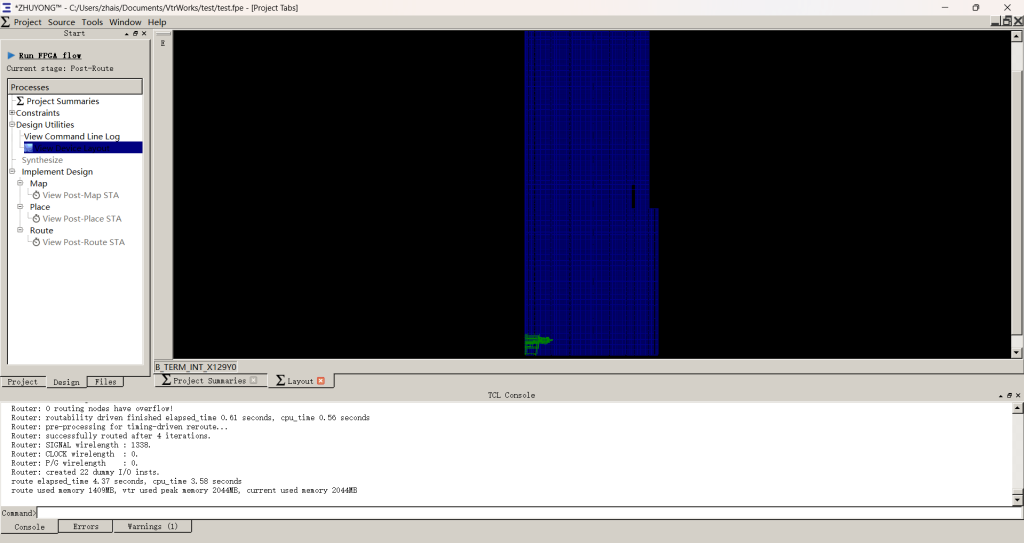

墨图(Motor)布局布线器

先进的异构FPGA EDA后端布局布线工具,专为满足现代复杂多样的FPGA硬件架构设计需求而设计。其高效的算法和灵活的配置参数能够显著缩短设计收敛时间,提高设计效率。

FPGA EDA后端布局布线

- 布局布线算法:使用先进的分析式布局布线算法,结合全局分层布局布线策略,实现高效的布局布线,缩短设计收敛时间。

- UCF约束处理:高效处理用户定义的物理和逻辑约束,确保满足特定需求的布局布线。

- SDC标准时序优化:时序驱动布局布线算法,优先处理关键路径,确保设计满足用户SDC时序要求。

- 物理综合:在布局布线过程中优化逻辑结构,提高设计时序性能。

- Tcl脚本支持:支持Tcl脚本编写,实现自动化布局布线,提高设计效率和一致性。

- 并行算法:采用并行布局布线算法,提高布局布线速度和效率。

- 拥塞管理:通过拥塞预测和管理技术,实时检测并处理拥塞区域,优化布线资源利用。

- 层次化设计:支持层次化设计方法,有效管理大规模设计,提高模块化和可维护性。

- GUI图形界面:提供直观的GUI,设计人员可通过可视化方式进行布局布线调试和优化。

- 可配置参数:提供多种可配置参数,允许用户根据具体设计需求调整算法行为,灵活适应不同复杂度和规模的设计。

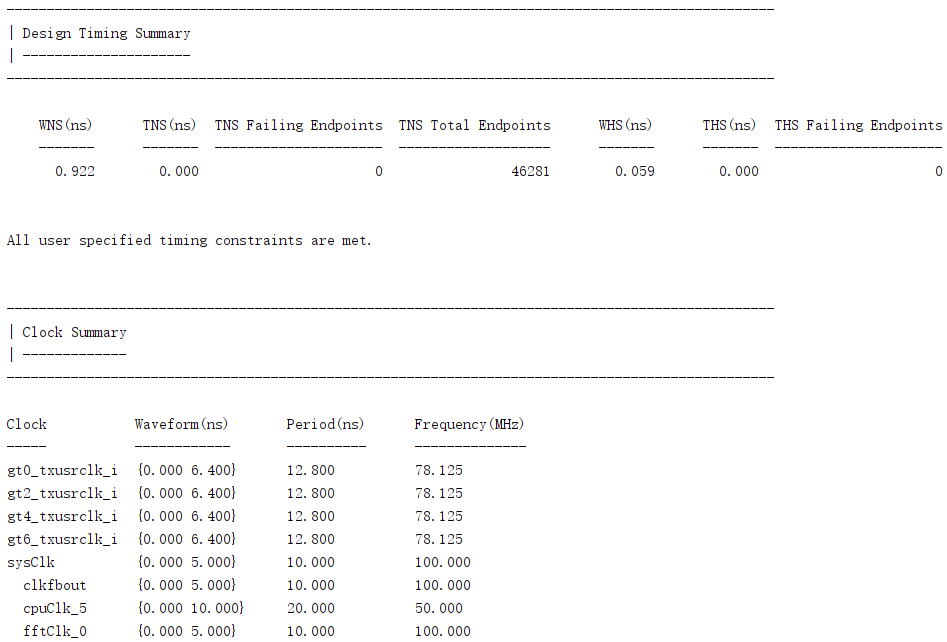

墨时(Mosis)时序分析器

高效的静态时序分析工具,旨在帮助EDA工具进行快速时序分析获取详细时序信息,以及帮助设计人员快速识别和解决时序违规问题,确保设计的时序可靠性。

STA静态时序分析

- 图方法建模:使用基于图的方法建模时序路径和依赖关系,高效传播时序信息,快速识别关键路径。

- 标准格式支持:支持SDC (.sdc)、Liberty (.lib)等行业标准格式,无缝集成到现有设计流程中。

- PVT时序模型:支持考虑工艺、电压和温度变化的高级时序模型,确保时序分析准确反映电路的实际工作条件。

- 详细时序报告:提供包括关键路径分析、TNS、WNS等详细时序报告,帮助设计人员快速识别并解决时序违规问题。

- 增量分析:支持增量式时序分析,仅对变化部分进行重新分析,显著提高时序分析速度。

- 并行处理:利用多核处理器,将时序分析任务分配到多个核心上进行处理,增强性能,缩短分析时间。

- 命令行界面:提供用户友好的命令行界面,并支持Tcl脚本编写,方便自动化重复任务

6大优势

CONTACT US

上海筑永科技有限公司

地址: 上海市闵行区紫星路588号2幢3楼330室

Email:zhuyong@zhuyongeda.com

网 址:www.zhuyongeda.com

微信:zhuyongeda